基于FPGA的图像采集与存储系统设计论文

2023-09-24 11:24:31 来源:SCI论文网 作者:wangye

摘要:高分辨率传感器应用越来越广,但超高清分辨率图像会带来高带宽、高存储、高码流等一系列问题。针对这些问题,提出一种基于FPGA的图像采集与存储系统的设计方案。在硬件设计上,以FPGA、NVMe SSD固态硬盘、DDR、CMOS为核心器件,通过FPGA芯片实现对CMOS、DDR、NVMe SSD固态硬盘的驱动控制功能,以实现图像数据的采集、高速缓存、高速存储等功能;通过千兆网将图像数据传输到PC端进行解码、显示等操作。利用FPGA实现对图像数据流的控制,可最大限度发挥FPGA芯片的性能,保证高分辨率图像传输的实

摘要:高分辨率传感器应用越来越广,但超高清分辨率图像会带来高带宽、高存储、高码流等一系列问题。针对这些问题,提出一种基于FPGA的图像采集与存储系统的设计方案。在硬件设计上,以FPGA、NVMe SSD固态硬盘、DDR、CMOS为核心器件,通过FPGA芯片实现对CMOS、DDR、NVMe SSD固态硬盘的驱动控制功能,以实现图像数据的采集、高速缓存、高速存储等功能;通过千兆网将图像数据传输到PC端进行解码、显示等操作。利用FPGA实现对图像数据流的控制,可最大限度发挥FPGA芯片的性能,保证高分辨率图像传输的实时性、稳定性、高效性。从硬件设计、软件设计、测试试验等方面,对图像采集与存储系统进行了说明并进行了试验。结果表明:利用该系统最终采集到了分辨率为9120像素×7000像素的图像,该系统可实现的存储速度为608 MB/s,实现了9 K以上分辨率的图像采集和存储。

关键词:超高清成像;FPGA;图像采集;图像存储、

Design of Image Acquisition and Storage System Based on FPGA

Abstract:High resolution sensors are more and more widely used,but ultra HD resolution images will bring a series of problems such as high bandwidth,high storage and high bit stream.To solve these problems,a design scheme of image acquisition and storage system based on FPGA was proposed.In terms of hardware design,with FPGA,NVMe SSD,DDR and CMOS as the core devices,the drive control functions of CMOS,DDR and NVMe SSD were realized through FPGA chip,and then the image data acquisition,cache,high-speed storage and other functions were realized;the image data were transmitted to the PC end through the Gigabit network for decoding,display and other operations.The control of image data stream by using FPGA can maximize the performance of FPGA chip and ensure the real-time,stability and high efficiency of high-resolution image transmission.The image acquisition and storage system was described and tested from the aspects of hardware design,software design,test and experiment.The results show that by using the system,the image with a resolution of 9120 pixel×7000 pixel can be acquired,the storage speed can be 608 MB/s,and the image acquisition and storage of more than 9 K resolution is realized.

Key words:ultra high definition imaging;FPGA;image acquisition;image storage

0引言

近年来,视频产业迎来了爆发式的增长,图像采集技术作为人类视觉的延伸,被广泛应用于人们的生活中,在机器视觉、智能工业、智能医疗、视频安防、电视直播等领域有着十分广泛的应用。在电视直播领域,通过超高清大屏,可以带给人们极致的视觉体验;在安防监控领域,通过超高清视频监控设备,可以提升城市安全;在医疗健康领域,通过超高清内窥镜设备,可以更清楚地检测人体内部情况。同时,随着5G技术的发展与普及,超高清成像技术与5G技术结合应用的前景也十分可观。图像作为一种信息,比其他信息更加能够体现出实物的实际状态[1-4]。随着传感器技术的发展,CMOS图像传感器的分辨率、灵敏度、帧频都有了显著的提升,并发展出了高清、高速摄像机。相比于传统摄像技术,高清、高速摄像设备产生的数据量巨大,因此对图像传输、存储都提出了较高的要求。

传统的图像采集技术大多是以单片机或DSP作为核心器件,对数据进行操作时,主要是串行处理,对于数据量较大、实时性要求较高的场合,传统的图像采集技术则无法满足要求。传统的数据主要通过SD卡、SATA机械硬盘等方式存储,其读写速度、稳定性较差,对于高稳定性、高实时性的场合则无法满足要求[5-7]。

对于超高分辨率图像采集及存储,传统的设备无法满足传输的实时性、高效性、稳定性等要求[8-9],为此本文提出将FPGA作为主控芯片,高分辨率CMOS作为成像芯片,NVMe SSD固态硬盘作为存储介质,实现高清图像数据的采集及存储。FPGA芯片作为一种现场可编程门器件,具备大规模数据流并行处理能力,通过外挂DDR缓存设备,可以实现数据的高速传输、缓存等功能。NVMe SSD固态硬盘支持PCIe协议,可实现数据的高速写入和存储,能够达到高精度、无损、大数据量地采集目标[10]。

1系统总体设计方案

本文在进行系统硬件设计时,主要考虑图像采集和图像存储2个方向。其中,图像采集的目标是获取超高清图像数据,在设计时,考虑的图像分辨率为9 K以上,存储时长不少于30 min。

利用CMOS进行成像时,需要搭配镜头共同使用。因此,在设计硬件方案时,对于电路板,将CMOS板卡和主控板卡独立开来。系统硬件总体结构如图1所示,它由2块板卡组成,分别为CMOS板卡和图像采集与存储板卡,通过柔性电路板连接2块板卡,能够提高系统的容错性;在安装镜头时,可任意改变2块板卡之间的角度,便于安装和固定。

硬件功能实现的核心是图像采集与存储板卡,按照功能可将其划分为主控模块、缓存模块、存储模块、传输模块、电源管理模块。具体功能如下:

(1)主控模块是整个系统的控制核心,主要实现图像数据流的采集、缓存、存储以及板卡上各芯片的驱动控制功能;

(2)缓存模块主要用于实现图像数据的缓存,将图像数据高速写入到存储介质中;

(3)存储模块是图像数据的存储介质;

(4)传输模块可将存储下来的图像数据传输到PC端,进行解码、处理等操作;

(5)时钟管理模块为板块上芯片工作提供所需要的时钟频率;

(6)电源管理模块的板卡采用12 V供电,经电源转换模块转换为板卡上各芯片所需要的工作电压。

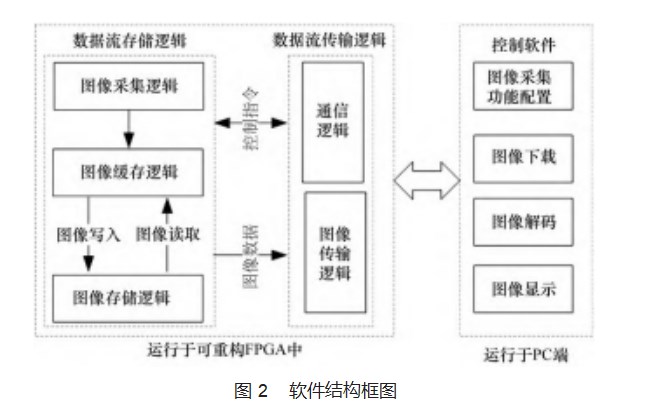

为充分发挥整个图像采集与存储系统的工作性能,将软件分为两部分进行设计,分别为上位机软件和下位机软件。其中,上位机软件运行于PC端,提供良好的人机交互界面,负责完成图像采集和存储的相关功能配置;下位机软件运行于可重构FPGA中,主要负责整个系统的数据流管理及板卡上各接口的时序控制功能。

2系统硬件设计

2.1 CMOS传感器选型

CMOS图像传感器由于低成本、体积小及功耗低的特性,在图像采集系统领域中应用十分广泛[11]。本文的设计目标是获取9 K分辨率的图像数据并进行存储,通过调研国内CMOS厂家,某公司生产的GAMX3265符合本次设计要求,可实现最高分辨率为9 520像素×7 000像素的图像数据输出。

GMAX3265传感器可通过SPI协议实现参数配置和分辨率、积分时间、增益、开窗等参数调节功能。为降低开发成本并减少存储介质的使用数量,将CMOS传感器设置为外触发工作模式,分辨率为9 120像素×7 000像素,帧频为10 Hz。

系统工作时,传感器内部序列发生器产生图像获取所必须的时序信号,像素曝光后,生成图像信号,通过传感器的LVDS通道输出图像数据[12-13]。

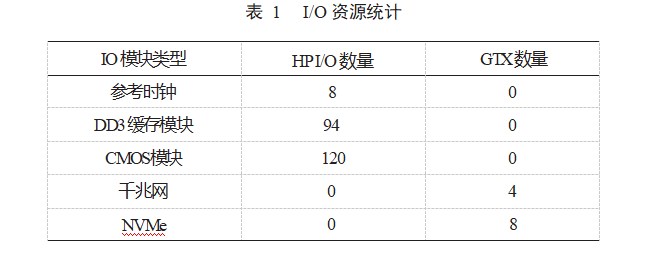

2.2主控芯片选型

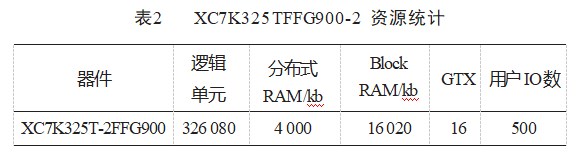

FPGA芯片是整个系统的控制核心,通过运行在FP⁃GA芯片上的控制逻辑,实现图像数据流的传输控制以及各接口的驱动功能。在芯片选型时,本文主要考虑系统所需要的硬件资源,包括高速收发器数量、I/O接口数量。系统所需要的硬件资源如表1所示。

本次设计采用的FPGA芯片为赛灵思公司的XC7K325TFFG900-2芯片,其硬件资源情况如表2所示,能够满足系统需求。

2.3 DDR芯片选型

对于DDR芯片的选择,主要考虑DDR芯片能够提供的数据带宽及缓存空间。DDR上游为图像输入模块,本文所要获取的图像分辨率为9 120像素×7 000像素,帧频为10 Hz,因此瞬时最大带宽为6 Gb。DDR下游为图像存储模块,在进行设计时,需要保证采集到的图像数据全部存储下来,因此DDR下游读取速度至少为6 Gb。由于DDR写入和读取采用的是相同的数据线,DDR工作过程中需要提供的带宽至少为12 Gb,本文选择镁光公司的MT41J128M16JT-125IT作为缓存芯片,单片DDR芯片的容量为2 Gb,支持的最高传输速率为1 600 MT/s,最大接口带宽为25 Gb,能够满足DDR上下游图像传输所需带宽。

在图像缓存策略上采用3帧缓存,因此DDR至少需要提供3帧的缓存空间,通过计算可知,单张照片数据量约为500 Mb,单片DDR3能够提供3帧图像的缓存空间。

综上可知,MT41J128M16JT-125IT能够提供的传输带宽及容量均能够满足本文的设计需求。

2.4存储介质选型

在选择存储介质时,主要考虑读写速度和存储空间两方面。

固态硬盘凭借体积小、功耗低、噪声低、速度快、抗振性好等特点,被广泛应用在各个领域[14]。针对本文设计需求,读写速度对于超高清图像存储设备来说是十分关键的性能指标,如果速度过慢,则无法保证图像数据全部存储下来,本文选择三星公司的970EVO Plus NVMe SSD固态硬盘,在性能上能够满足本次设计要求。

NVMe SSD固态硬盘通过PCIe2.0×4模式与FPGA之间进行数据传输,单通数据传输速率可达到4 Gbps,能够满足DDR高速写入的要求。

单块NVMe SSD固态硬盘的存储空间为2 T,本文的目的是记录至少30 min超高清图像数据。对于分辨率为9 120像素×7 000像素,帧频为10 Hz的图像数据,每秒钟产生的数据量为6 Gb,本文采用1块2 TB的NVMe SSD固态硬盘作为存储介质,可最多存储45 min的超高清图像,能够满足设计要求。

为将NVMe SSD固态硬盘中的数据导出解析,在设计硬件时增加了千兆网口,通过千兆网和PC端实现数据交互,通过上位机软件控制图像采集与存储板卡进行工作,获取NVMe SSD中存储的图像数据,实现对数据的解码及图片生成功能。

3系统软件设计

软件结构框图如图2所示,运行于FPGA中的下位机软件由两部分组成,分别为数据流存储逻辑和数据流传输逻辑。其中,数据流存储逻辑包括图像采集逻辑、图像缓存逻辑、图像存储逻辑;数据流传输逻辑包括图像传输逻辑、系统通信逻辑。运行于PC端的上位机软件,主要功能为图像采集功能配置、图像下载、图像解码、图像显示等功能。

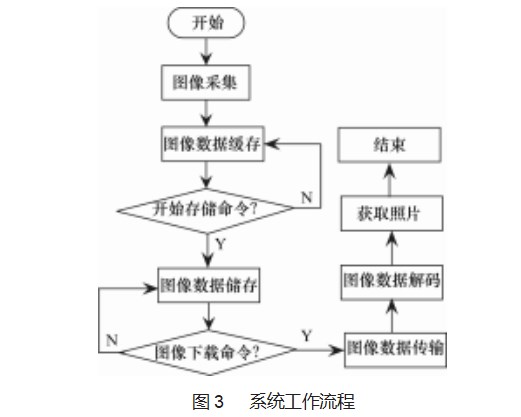

系统工作流程如图3所示。系统运行后,首先完成系统初始化操作,当CMOS开始输出图像数据后,图像采集逻辑会将图像数据缓存至DDR中,如果上位机软件没有发出图像存储指令,则数据会持续写入DDR中,DDR中始终缓存最新的3帧图像数据;当上位机控制软件发出开始存储命令后,图像数据开始写入SSD固态硬盘中;当发出停止存储指令后,最后1帧数据写入完成后,系统即停止存储图像数据。存储的图像数据可通过千兆网下载到PC端,经过上位机软件解码后,获得图像。

3.1 FPGA逻辑设计

3.1.1数据流存储逻辑设计

(1)图像采集逻辑设计

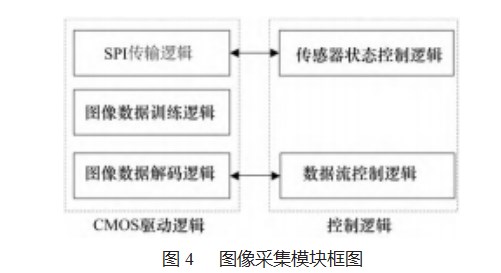

如图4所示,图像采集逻辑主要由两部分组成,分别为CMOS驱动逻辑及模块控制逻辑。其中,CMOS逻辑主要负责完成CMOS传感器的驱动控制,使它按照配置要求输出图像数据;模块控制逻辑主要控制传感器的状态,根据需求更改CMOS的参数配置,数据流控制逻辑将解码后的图像数据传递到图像缓存模块中。

图像采集模块的核心功能是获得图像数据,首先通过SPI协议完成对CMOS的驱动控制,然后传感器开始输出图像数据,通过图像采集模块的训练及解码逻辑,将获得的图像数据输出到图像缓存模块[15]。

通过SPI协议可实现对传感器各功能寄存器的配置,其中比较关键的为图像分辨率的设置、积分时间的设置、增益的设置、触发模式的设置。为降低数据量,提高存储时长,在设置触发模式时,选择了外触发模式,并将帧频控制在10 Hz;在设置图像分辨率时,选择的分辨率为9 450像素×7 000像素。在图像数据解码逻辑部分,本文截取了图像数据,输出高8位图像数据,同时将每行的数据截取为9 120个像素。

(2)图像缓存模块

考虑到超高清图像数据量较大,如果只通过FPGA片上BRAM资源进行缓存,难以实现图像数据的正常缓存,同时为了提高数据的传输速度,选择在DDR上实现图像数据的缓存。在硬件上本文选择一片2 Gbit 16bit的DDR芯片。

图像缓存模块由DDR控制器写入逻辑、DDR控制器读取逻辑两部分组成。系统开始工作后,首先进行DDR初始化操作,当初始化完成后,系统开始等待数据写入,通过DDR控制器将逻辑控制数据写入到不同的缓存区,当数据缓存完成后,通过DDR控制器读取逻辑读取存放在缓存区的图像数据。DDR工作流程如图5所示。

在设计DDR读取逻辑时,通过Vivado提供的MIG IP进行设置,基于MIG IP核设计的DDR读写时序简单[16],其中IP核输出的关键信号有app_rdy、app_addr、app_cmd、app_wdf_data、app_rd_data_valid等[17]。在对DDR进行读取操作时,app_rdy为十分关键的信号,它表示当前DDR是否为可操作状态,当其为1时,表示DDR可以开始读取操作。如果在图像数据写入时,时序控制得不好,app_rdy信号会反复拉低,降低了DDR的工作效率。为提高DDR的读取效率,避免app_rdy信号反复拉低,在图像数据写入前,采取了乒乓操作。

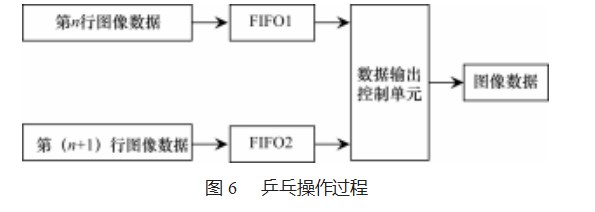

乒乓操作过程如图6所示。采用2个相同位宽、相同深度的异步FIFO,当FIFO1中一行图像数据缓存完成后,通过数据输出控制单元将FIFO1中的图像数据写入到DDR中,此时新产生的图像数据写入FIFO2中。当FIFO1中图像数据被读空后,DDR进入等待状态,直到FIFO2中缓存完一行图像数据,然后开始读取FIFO2中的图像数据,此时图像采集模块将解码后的图像数据写入到FIFO1中进行缓存,依次交替进行,这样可以大大提高DDR的读取效率。

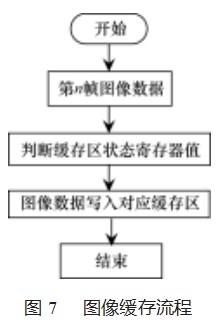

图像数据写入DDR的流程如图7所示。本文在设计DDR缓存逻辑时,采取了3帧缓存策略,将DDR空间划分为3个缓存buf⁃fer空间,分别为buffer1、buf⁃fer2、buffer3,设置了2个状态寄存器参数buffer_full和buffer_emp⁃ty,分别对应3个缓存区的空满状态。图像传输开始后,根据2图7图像缓存流程个寄存器的值确定当前缓存区的状态,当buffer_full和buffer_empty均为0时,表示缓存区为空,当前系统还没有进行图像数据的写入或者读取操作,当buffer_full为1且buffer_empty为0时,表示当前DDR3中已经缓存了1帧图像数据,此时还没有1帧图像数据被读取;当buf⁃fer_full为3且buffer_empty为1时,表示buffer3中图像数据为最新一帧,buffer1图像数据已经读取完成,此时若进行读写操作,应该向buffer1中写入图像数据,读取buffer3中图像数据。如此,可根据状态寄存器的值选择数据读取和写入的缓存buffer空间。

当DDR中的图像数据已经缓存完一帧后,DDR才可以向外输出图像数据,当前buffer空间的一帧图像数据读取完毕后,才会再次向该buffer写入图像数据。如果系统没有发出存储指令,DDR中的图像数据始终不会向下游模块输出,新写入的图像数据会反复覆盖3个缓存空间,其中buffer_full的值始终指向最新一帧图像数据所在空间。

(3)图像存储逻辑

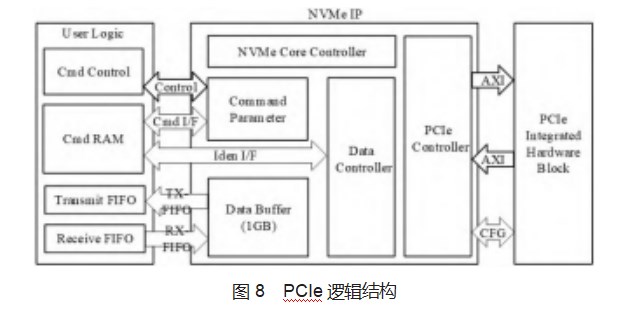

本文选取1块NVMe SSD固态硬盘作为图像数据的存储介质,通过NVMe规范实现对SSD固态硬盘的驱动控制,在FPGA内实现NVME的主机控制[18],其逻辑总体方案如图8所示。协议的传输层采用Xilinx提供的PCIe硬核实现,PCIe硬核的控制器和NVMe协议的应用层由NVMe的控制器模块实现,应用层以上的部分由FPGA内其他模块实现[19]。

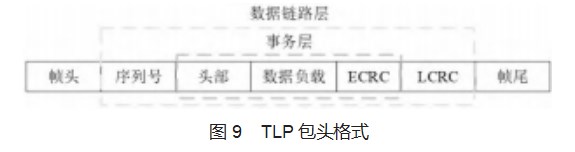

PCIe协议实现的核心是将数据打包为TLP包,通过GTX发送。TLP包格式如图9所示。

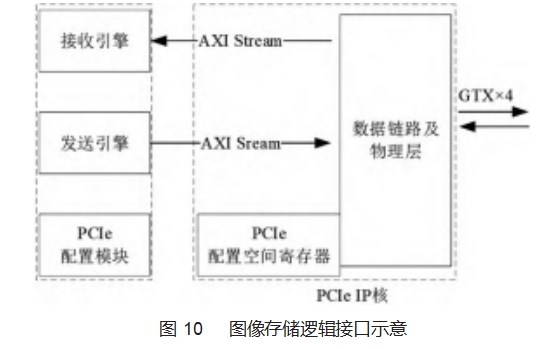

图像存储逻辑接口如图10所示。PCIe控制器内部包括接收引擎、发送引擎以及PCIe配置模块三部分。其中,发送引擎接收来自DDR缓存的图像数据,将其打包为TLP包,通过AXI协议发送PCIe核;接收引擎将来自PCIe核的TLP数据包进行解析,发送至图像数据传输模块,最终传输到上位机。

3.1.2数据流传输逻辑

数据流传输逻辑功能分为两部分,分别为图像数据流传输及控制信号传输,传输的物理通道是千兆网。千兆以太网具有实时性强、传输速度快、可移植性好等特性[20]。

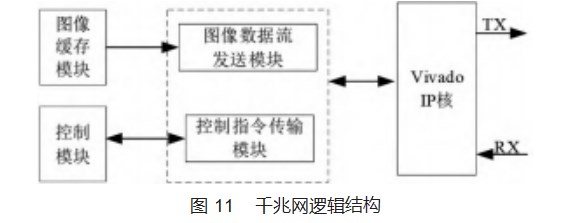

图像数据流传输是将存储在NVMe SSD固态硬盘中的图像数据传输到PC端,通过上位机软件进行解码、显示等操作。控制信号传输主要传输的是CMOS传感器的配置参数、NVMe SSD固态硬盘的配置参数。千兆网逻辑结构如图11所示,其中针对本次设计采用的是SGMII IP核,MAC层使用Tri Mode Ethernet MAC IP核,通过图像数据流发送模块和控制指令传输模块,将需要发送的数据发送到IP核,或者将IP核接收到的数据传递到相应模块进行解析。

3.2上位机软件设计

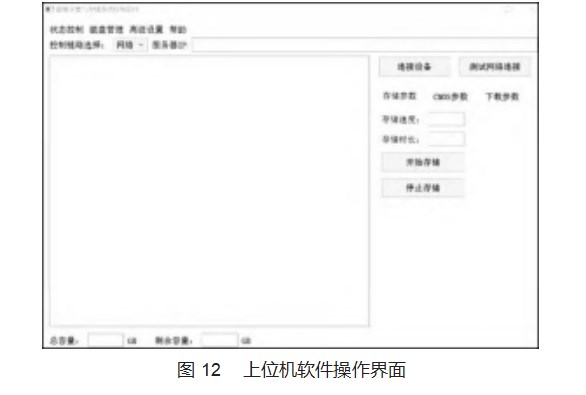

上位机软件提供图像采集与存储的监控界面,通过更改上位机软件配置参数,可实现对CMOS传感器的配置操作,从而更改积分时间、增益等参数。通过上位机软件下载功能,可读取存储在NVMe SSD固态硬盘中的数据,通过上位机软件的解码功能,可显示出采集到的图像数据,其操作界面如图12所示。

4测试试验与结果分析

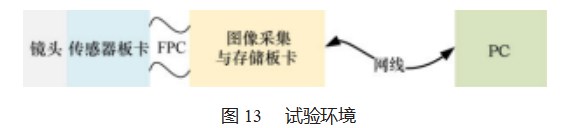

根据本文目标,在对系统性能进行验证时,主要验证图像分辨率、存储速度、存储时长等指标。采用如图13所示的测试方式,将镜头对准空旷的室外进行拍摄,将图像采集与存储板卡通过千兆网口与计算机相连接。试验开始后,首先输入IP地址,将板卡与计算机通过网络进行连接,连接完成后,对CMOS传感器工作参数进行设置,主要设置积分时间、增益等参数,参数设置完成后系统即可开始工作。点击开始存储后,图像数据开始存储到NVMe SSD固态硬盘中,点击停止存储后,图像数据停止写入到NVMe SSD固态硬盘中,通过系统状态监测区域,可以监测到当前存储速度、存储时长等参数。

如图14所示,在试验过程中,系统存储速度可以稳定在608 MB/S,单张分辨率为9 120像素×7 000像素的图像大小约为487 Mb,通过计算可知,当前帧频约稳定在12帧,能够满足设计要求。系统工作2 452 s后,存储容量约为2 012 GB,已经接近硬盘的最大存储容量。

通过上述试验可知,系统存储速度、存储时长均能够满足预期设计要求。图像存储完成后,通过千兆网传输到PC端,以二进制文件形式存储,同时通过抽行抽列的方式,将图像数据显示在操作软件上。

对存储1 s的图像数据进行了解码,解码后获得的图像数据如图15所示,共获得10张高分辨率图像。

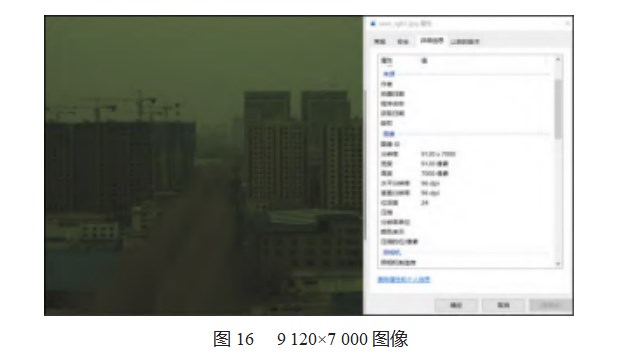

单张图像信息如图16所示,其分辨率为9 120像素×7 000像素,图像分辨率满足本次设计要求。

经过上述试验验证,本文所述的图像采集与存储系统能够实现9 K以上分辨率图像采集,存储时长能够达到40 min以上。

5结束语

针对超高清图像数据的采集与存储,本文在硬件设计上以FPGA、NVMe SSD固态硬盘为核心器件,利用FPGA大规模并行数据的处理能力,实现图像数据流传输。利用NVMe SSD固态硬盘实现图像数据的高速存储;利用千兆网实现图像数据的导出。在软件设计上,为了充分发挥系统性能,在FPGA中运行数据流控制逻辑,在上位机软件进行图像解码、系统控制等操作。经过试验,成功获取了分辨率为9 120像素×7 000像素,帧频为10帧的图像数据,同时试验也证明了系统可存储40 min的图像数据。后面应用过程中,可针对不同应用场景对本系统进行升级改造,通过增加NVMe SSD固态硬盘数量实现更长时间的数据存储功能,通过增加机械设计,满足系统不同场景下的安装、固定等要求。

[1]栾天.基于FPGA的8K智能投影融合平台系统设计[D].上海:华东师范大学,2022.

[2]宋梦欣.基于FPGA的多路超高清摄像头控制器设计[D].上海:华东师范大学,2022.

[3]金祥.基于FPGA的多功能图像采集存储系统设计[D].西安:西安电子科技大学,2020.

[4]康宇.基于CMOS传感器的图像采集处理系统设计与实现[D].太原:中北大学,2021.

[5]龚涛.基于FPGA的图像采集处理系统[D].武汉:华中科技大学,2005.

[6]高丽燕.基于DSP+FPGA的图像识别系统设计与实现[D].南京:南京理工大学,2006.

[7]连成哲,翟东奇,蒋沅嵩,等.基于ZYNQ的高清视频与图形叠加显示技术[J].计算机技术与发展,2022,32(4):74-79.

[8]王伶杰.基于FPGA的大面阵背照式sCMOS相机系统设计[D].广州:中国科学院大学(中国科学院光电技术研究所),2021.

[9]马玉真,胡亮,方志强,等.计算机视觉检测技术的发展及应用研究[J].济南大学学报(自然科学版),2004(3):222-227.

[10]WIELGOSZ M,PIETRON M,KARWATOWSKI M,et al.Real time 8K video quality assessment using FPGA[J].Pomiary Au⁃tomatyka Kontrola,2016,62(6):187-189.

[11]ZHAI G F.Pixel response non-uniformity correction for multi-TDICCD camera based on FPGA[C]//Proceedings of Image and Signal Processing for Remote Sensing XIX,2013.

[12]闫宏亮.基于万兆网的激光通信测试系统设计[D].哈尔滨:哈尔滨工业大学,2021.

[13]张程杰.基于FPGA-PCIE的声发射信号采集系统研究[D].太原:中北大学,2022.

[14]黄纬然.基于FPGA及DDR3的高速存储系统设计与实现[D].沈阳:沈阳化工大学,2021.

[15]周艳.SSD控制器中的PCIe_DMA的设计与实现[D].西安:西安电子科技大学,2021.

[16]WANG L,WANG J,ZHANG Q.Design and implementation of DDR SDRAM controller based on FPGA in satellite navigation system[C]//Proceedings of 2012 IEEE 11th International Con⁃ference on Signal Processing,Beijing,2012:456-460.

[17]郜嘉铭.基于PCIe2.0的高速发送器设计[D].沈阳:辽宁大学,2022.

[18]LI C Y,LIU H T,YANG Z Q,et al.FPGA implementation of a L-band digital aeronautical communications system(L-DACS1)physical layer(PHY)[C]//Proceedings of 2013 Interna⁃tional Conference on Mechatronic Sciences,Electric Engineer⁃ing and Computer(MEC),Shengyang,2013:3227-3230.

[19]殷平天,赵福海,吴侠义,等.ZYNQ与NVME协议的模块化存储系统设计[J].单片机与嵌入式系统应用,2023,23(2):76-79.

[20]王笑寒,韩文波.基于FPGA+DSP的高清视频监控系统研究[J].长春理工大学学报(自然科学版),2022,45(6):67-72.