基于 FPGA 窄脉冲信号发生器的设计论文

2025-07-30 15:36:26 来源: 作者:xuling

摘要:针对电子感应加速器的俘获效率提升较低问题,考虑到运用电子电路方法产生的脉冲电流信号作用于俘获线圈会带来温度变化、电磁干扰等影响,设计了一个基于FPGA可编程的窄脉冲信号发生器。

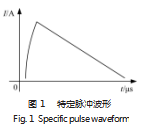

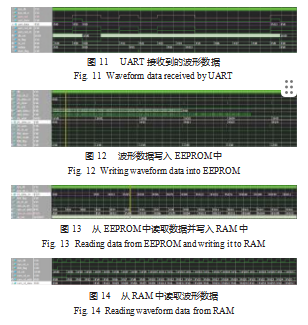

摘要:针对电子感应加速器的俘获效率提升较低问题,考虑到运用电子电路方法产生的脉冲电流信号作用于俘获线圈会带来温度变化、电磁干扰等影响,设计了一个基于FPGA可编程的窄脉冲信号发生器。通过模块化设计,能够输出满足需求且稳定的特定脉冲波形,该脉冲波形的周期为300μs,脉冲宽度在3μs左右,波形上升部分呈指数型曲线,响应时间很快,下降部分则呈线性衰减。利用串行通信,可以将符合要求的波形数据(以TXT文件形式保存)一次性写入FPGA的EEPROM中,这样首先保证了掉电后数据不会丢失,再从EEPROM中读写到RAM IP核中,最后从RAM IP核中把波形数据读取出来。结果表明:运用MODESIM仿真,仿真结果与上板验证过程基本一致,可以很好地输出目标波形,验证了该脉冲信号发生器的可行性。

关键词:电子感应加速器;FPGA;可编程脉冲信号发生器;EEPROM;RAM IP核

0引言

目前,国内在用的电子感应加速器大部分属于进口,此类加速器的关键技术并未公开,针对加速器的电子俘获效率的关键性科学技术难题进行研究,实现具有自主知识产权的电子感应加速器具有非常重要的意义。电子感应加速器是利用电磁感应原理来加速电子的一种加速器装置[1]。它的基本原理是利用随时间变化的磁通量产生的涡旋电场来加速带电粒子[2]。由于小型电子感应加速器被加速的电子数量与加速器产生的X射线辐射强度成正比,所加速的电子数量取决于被磁场俘获的电子数量[3-6],故在此着重讨论如何提升加速器的电子俘获效率。

东华理工大学核应用技术研究所利用了基于磁势阱[7]调控的方法来提升电子俘获效率。要实现磁势阱的调控必须在平衡轨道内部产生一个叠加磁通量,而叠加磁通是通过放置在平衡轨道上的线圈来产生的,工作时给线圈通一快速脉冲电流即可产生对应的磁通量。通过这种电路产生脉冲电流的方法得到的脉冲波形较为固定,不能灵活更改。

针对脉冲信号发生器的设计,研究者进行了大量研究。章欣[8]基于FPGA并运用DDS技术,通过模块化设计,使标准脉冲信号发生器能够产生1~100 kHz线性可调的脉冲。沈航[9]基于FPGA设计的任意波形信号发生器,利用下位机和上位机两部分,可以产生0.01 Hz~10 MHz的任意波及正弦波、方波、三角波等常规的函数信号。杨大伟等[10]设计了基于FPGA的直接数字频率合成多信号发生器的基本组成和设计原理,使用VHDL编程,在Quartus II中进行了仿真,实现了正弦波、锯齿波、方波、三角波等的频率可调、相位可调、幅值可调等功能。

但是以上研究结果多少输出常规的脉冲波形,对加速器的研究应用效果并不好。因此要让脉冲信号发生器产生符合加速器需求的波形尤为重要。

本文在此基础上,基于FPGA脉冲信号发生器来产生特定的脉冲波形,该特定脉冲波形上升时间很快,下降部分呈线性衰减,如图1所示。若产生的脉冲波形不符合要求,可以随时进行编程修改,以满足项目需要。从而能保证更多的电子进入到平衡轨道上,提升电子俘获效率,进而增强加速器的辐射强度。

1系统总体方案

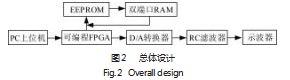

本文设计的可编程脉冲信号发生器基于FPGA,在FPGA中设计各个模块电路,用Verilog硬件描述语言来编写程序实现模块的功能。在进行硬件设计时,主要考虑的方面是波形数据的传输与储存。总体脉冲信号发生器的设计由PC上位机、串行通信、EEPROM模块、双端口RAM、DAC模块、RC低通滤波构成。其中波形数据的传输是通过串行通信接口UART来实现,波形数据的存储是通过EEPROM和RAM来完成。

上位机通过UART接口将波形数据(256个8位的波形数据且保存在TXT文件中)写入EEPROM中,因为EEPROM有掉电后数据保存的特性。然后再写入RAM中,最后从RAM中读取出来,因为相较于EEPROM,RAM的读写速度非常快。这样既能确保掉电后数据不丢失,又能保证波形的读取速度。

读取后的数据经过DAC模块,将数字信号转换成模拟信号,外接一个RC低通滤波器用于滤波处理,最后将波形数据输出,显示在示波器上。总体设计方案如图2所示。

2硬件模块设计

2.1主控芯片

由于在数据处理时需要MCU具备较高的并行处理能力,且针对数据要采点处理,因此选用了ALTERA公司的CycloneⅣ系列的EP4CE10F17C8可编程器件作为主控芯片来处理电流、电压以及内部运算等[11-12]。该可编程芯片功能强大,I/O端口丰富,拥有10 K的逻辑单元,179个可配置的I/O端口,414 KBit的嵌入式RAM资源,两个独立PLL锁相环,最大工作频率250 MHz。本设计采用输入时钟为50 MHz的有源晶振提供系统时钟信号,再结合其高性能和低功耗的特点,完成能够输出满足条件的特定脉冲信号。

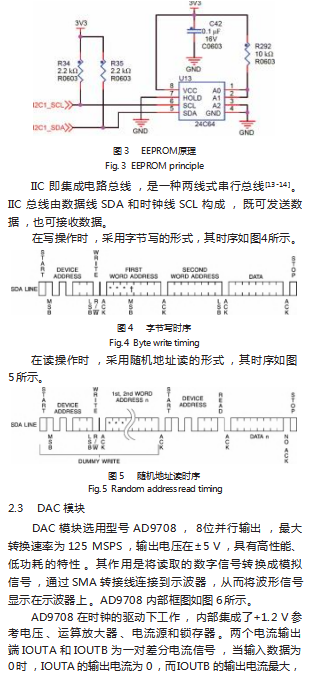

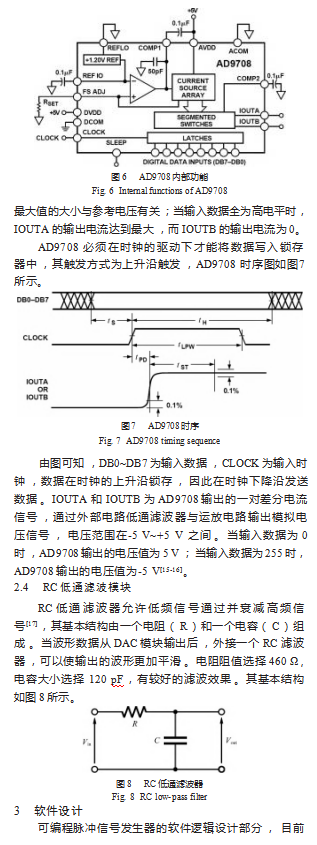

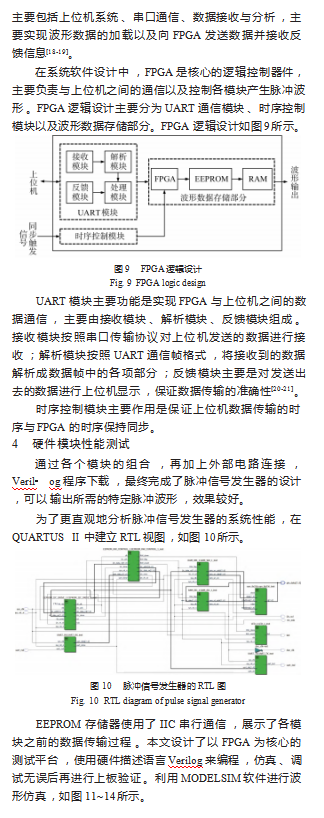

2.2 EEPROM与IIC通信

FPGA板载的EEPROM芯片(AT24C64),容量为64 Kbit。FPGA通过IIC总线与该芯片进行通信,可读可写,掉电数据不丢失,用于存储一些掉电不能丢失的重要数据。上位机通过串口将波形数据存入EEPROM中,EEPROM原理图如图3所示。

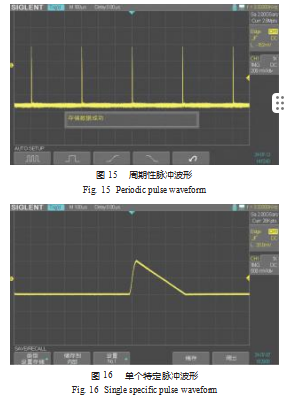

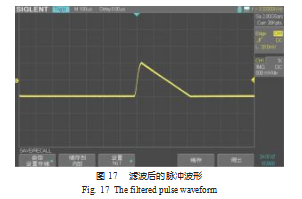

仿真结果满足要求。上板验证并且使用鼎阳科技SI⁃GLENT—SDS 2102高精度示波器对其进行测试。从图15中可以看出周期性波形每间隔300μs发射一次脉冲,图中一格为100μs,满足设计的要求。图16中是放大后的单个波形,可以看出,脉冲宽度为3μs左右,下降部分呈线性衰减,但是可以很明显有锯齿的干扰。图17是外接RC滤波器后的结果,在一定程度上减少了高频干扰,使得脉冲波形更平滑一些。

5结束语

本文基于FPGA进行了窄脉冲信号发生器的设计,输出的脉冲宽度为3μs,脉冲信号间隔300μs,且使用仿真软件MODESIM进行了波形仿真,仿真结果很好地显示了EEPROM与RAM读写波形数据的情况。上位机通过UART串行通信与FPGA之间进行数据传输,其传输的时序、逻辑均无差错。由于使用了EEPROM,当每次上电后,数据依旧被保存,并且波形数据一次性写入EE⁃PROM中的时间极短,为后续的加载所需波形提供了方便。因此相比于之前的电子电路方法,通过脉冲信号发生器输出的窄脉冲,具有可编程性、稳定性、抗干扰性等优点。本设计在提高电子感应加速器的俘获效率方面提供了数据参考和可行性方案。

参考文献:

[1]郑朔宇.电子感应加速器单粒子跟踪模拟计算[J].科技界,2018(5):10-11.

ZHENG S Y.Tracking simulation calculation of single particle in betatron[J].Science&Technology Vision,2018(5):10-11.

[2]陈佳洱.加速器物理基础(初版)[M].北京:原子能出版社,1993.

[3]Adams G D.A Method of Increasing Betatron Yield[J].Review of entific Instruments,1948,19(9):607-608.

[4]Kashkovskii V V.Dynamics of an electron beam in the magnetic field of a betatron[J].Russian Physics Journal,2004,47(12):1261-1267.

[5]Malikov E L,Shestak A P,Rychkov M M,et al.About the Elec⁃tron Charge Accelerated in the Small-size Betatron MIB-4[J].Journal of Physics Conference,2016,671(1):012034.

[6]Bess L,Hanson A O.Measurement of the Electron Current in a 22Mev Betatron[J].Review of Scientific Instruments,1948(2):108-110.

[7]Rajchman J A,Cherry W H.The electron mechanics of induc⁃tion acceleration[J].Journal of the Franklin Institute,1947,243(4):261-285.

[8]章欣.基于FPGA的脉冲信号发生器设计[J].气象水文海器,2014,31(2):69-73.

ZHANG X.Pulse signal generator based on FPGA[J].Meteorolog⁃ical,Hydrological and Marine Instruments,2014,31(2):69-73.

[9]沈航.基于FPGA的任意波信号发生器[D].西安:西安理工大学,2009.

[10]杨大伟,杨秀芳,陈剑虹.基于FPGA的DDS多信号发生器的设计与实现[J].西安理工大学学报,2013,29(4):439-443.

YANG D W,YANG X F,CHEN J H.Design and implementa⁃tion of direct digital frequency synthesis multiple signal genera⁃tor based on FPGA[J].Journal of Xi′an University of Technolo⁃gy,2013,29(4):439-443.

[11]黄振华.基于FPGA函数信号发生器的设计与实现[D].镇江:江苏大学,2009.

[12]何豆,孙恩昌,杨睿哲,等.海上无线SDMA接入的波束指向切换技术研究[J].移动通信,2024,48(9):160-165.

HE D,SUN E C,YANG R Z,et al.Research on Beam-Pointing Switching Technology for Maritime Wireless SDMA Access[J].Mobile Communications,2024,48(9):160-165.

[13]杨帆.基于I2C接口EEPROM读写控制器设计[J].微型机与应用,2015,34(10):22-24.

YANG F.Based on the I2C interface EEPROM read and write controller design[J].Microcomputer&Its Applications,2015,34(10):22-24.

[14]宁祎,王旭昊.一种基于I2C总线通讯的机器人舵机系统的设计[J].机电工程技术,2011,40(4):76-78.

NING Y,WANG X H.Design of robot servo based on I2C bus communication[J].Mechanical&Electrical Engineering Tech⁃nology,2011,40(4):76-78.

[15]寿开元.高分辨率高速DAC测试及优化方法研究[D].成都:电子科技大学,2023.

[16]秦晓伟,杜二旺,王国永,等.DAC采样时钟杂散对载波信号短期频率稳定度影响研究[J].时间频率学报,2018,41(3):214-218.QIN X W,DU E W,WANG G Y,et al.Influence of dac sam⁃pling clock spur on short-term frequency stability of carrier sig⁃nal[J].Journal of Time and Frequency,2018,41(3):214-218.

[17]王红霞,朱善林.单时间常数RC电路仿真分析[J].电子设计工程,2019,27(12):124-128.

WANG H X,ZHU S L.Simulation and analysis of single time constant rc circuit[J].Electronic Design Engineering,2019,27(12):124-128.

[18]徐碧辉,李廷凯,周加谊.一种快沿脉冲信号发生器的设计[J].电子设计工程,2016,24(18):66-68.

XU B H,LI T K,ZHOU J Y.A design of a fast pulse generator[J].Electronic Design Engineering,2016,24(18):66-68.

[19]马赵,任尚坤,杨梅芳.基于FPGA的电磁超声脉冲信号发生器的设计[J].微型机与应用,2016,35(23):83-85.

MA Z,REN S K,YANG M F.Design of electromagnetic ultra⁃sonic pulse signal generator based on FPGA[J].Microcomputer&Its Applications,2016,35(23):83-85.

[20]田宇,施赛烽,郑子贤,等.基于FPGA的高分辨率数字脉冲信号发生器的设计与实现[J].合肥工业大学学报(自然科学版),2020,43(2):224-226.

TIAN Y,SHI S F,ZHENG Z X,et al.Design and implementa⁃tion of high-resolution digital pulse signal generator based on FPGA[J].Journal of Hefei University of Technology(Natural Sci⁃ence),2020,43(2):224-226.

[21]孙玉辉.多模式雷达信号发生器的设计与实现[D].西安:西安电子科技大学,2023.